安装新浪财经客户端第一时间接收最全面的市场资讯→【下载地址】

卡住“英伟达的脖子”,他们卖爆了!

来源:华尔街见闻 常嘉帅

GPU之王的烦恼。

作为“掘金买铲”逻辑的核心受益者,英伟达创纪录的业绩,成了撑起生成式AI行情的信心支柱。

然而,隐匿于出色业绩背后,更关键的问题是,由于产能受限,英伟达无法满足市场对GPU的需求,8月曾有媒体报道,H100订单已经排队到了明年Q1甚至Q2。

根据GPU Utils的推测,保守估计,英伟达GPU潜在订单总额可能超过200亿美元,旗舰GPU H100的供给缺口高达43万张。

英伟达CEO黄仁勋也直言:

“我们目前的出货量远远不能满足需求。”

老黄的苦衷,就在于卡住英伟达脖子的两项关键技术——CoWoS封装和HBM内存。

SK海力士和台积电 卡英伟达脖子的幕后玩家

去年9月推出的H100,是英伟达产品矩阵中最先进的GPU。

相较于前任A100,它的价格翻了1.5-2倍左右,但性能却有了质的飞跃:推理速度提升3.5倍,在训练速度提升2.3倍;如果用伺服器丛集运算的方式,训练速度更是能提高到9倍。在LLM训练中,它能让原本一个星期的工作量,缩短为20个小时。

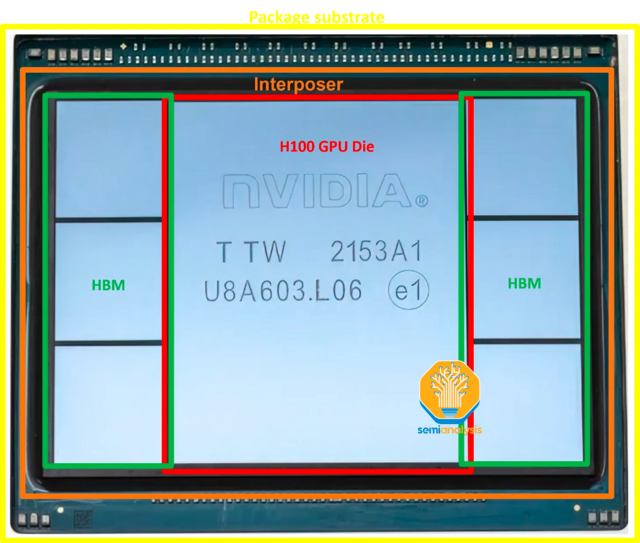

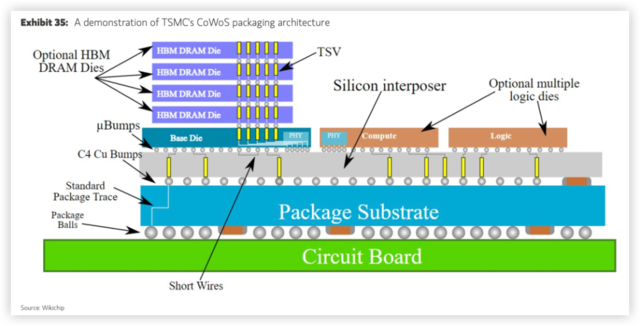

一块英伟达H100,主要由三个部分构成:中心的H100裸片两侧各有三个HBM堆栈,最外层则是台积电的2.5D CoWoS封装框。

三个部件里,核心的逻辑芯片供应是最简单的,它主要产自台积电台南18号工厂,使用4N工艺节点(实际是5nm+)。由于5nm+下游的PC、智能手机和非AI相关数据中心芯片市场疲软,目前台积电5nm+产能利用率不到70%。因此逻辑芯片供应没有问题。

英伟达最主要的供应缺口,来自逻辑芯片两侧的6块HBM(High Bandwidth Memory,高带宽内存),和把逻辑芯片、HBM连接起来的CoWoS封装(Chip on wafer on Substrate,芯片、晶圆、基板封装)。

HBM是一种基于3D堆叠工艺的DRAM内存芯片。其技术原理,就是将多个DDR芯片,垂直堆叠在一起,通过硅通孔(TSV)和微凸块(μBmps)技术,把芯片相互连接,从而突破了现有的性能限制,大大提高了存储容量,实现更高带宽、更高位宽、更低功耗、更小尺寸的DDR组合阵列。

内存芯片对GPU性能至关重要,尤其是训练AI所用的高性能GPU。推理和训练工作负载是内存密集型任务。随着AI模型中参数数量的指数级增长,仅权重一项就将模型大小推高到了TB级。因此,从内存中存储和检索训练和推理数据的能力决定了GPU性能的上限。AI大模型和应用越多,越有利于HBM制造商。

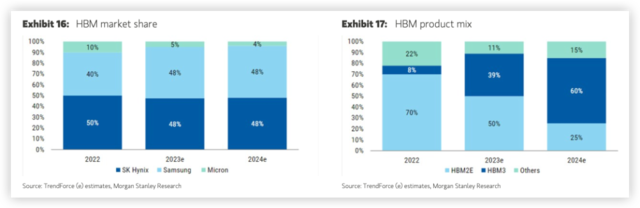

从整体HBM市场来看,两大韩国存储巨头SK海力士及三星占绝对垄断地位,二者合计市占率在90%左右。

英伟达H100上面使用的HBM3由SK海力士独家供应,这是目前最先进的HBM产品。

HBM3工艺复杂、成本高昂、产能有限,2022年,在整个HBM市场中,HBM3仅占约8%的市场份额。作为全球唯一有能力量产HBM3的公司,SK海力士牢牢卡住了英伟达H100的脖子;而前代 A100/A800以及AMD的MI200使用的则是落后一代的HBM2E技术。

不过,当前存储芯片业界正处于HBM2E向HBM3换代的过程中。据Trendforce数据,预计到2024年,HBM3市占率将超过60%,三星、美光等存储芯片厂都在积极布局,都对SK海力士的市场份额虎视眈眈。

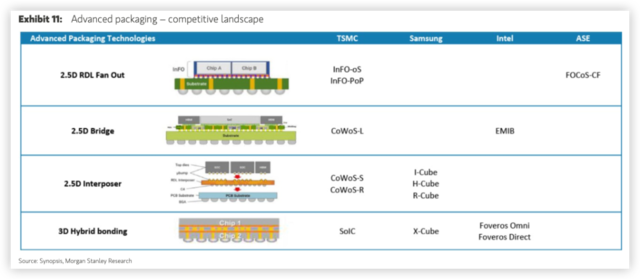

而先进封装则是一项与HBM内存相辅相成的技术——要用HBM堆栈,必须用先进封装把内存和GPU连接起来。

H100上使用的台积电CoWoS先进封装,是一项2.5D封装技术。

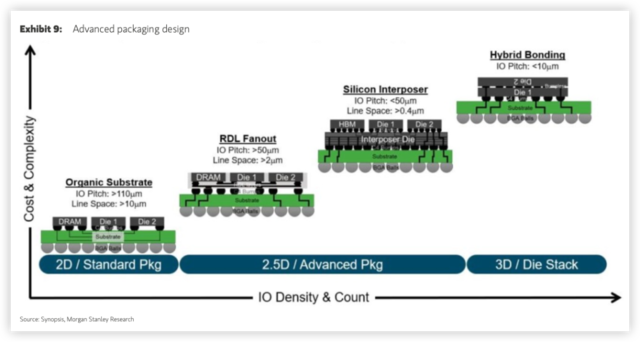

主流的2D封装方案,是在基板(Substrate)的表面水平安装所有芯片和无源器件的集成方式,类似于平面的拼图。

而2.5D先进封装,则可以类比为横向排列的积木。多层DDR芯片堆叠的HBM堆栈,必须依赖先进封装才能实现。

台积电的CoWoS先进封装方案,由CoW和oS组合而来:先将芯片通过Chip on Wafer(CoW)的封装制程连接至硅晶圆,再把CoW芯片与基板连接(on Substrate),整合成CoWoS。

CoWoS技术大大提高了互联密度以及数据传输带宽,同时缩小了封装尺寸,但工艺也非常复杂,因此主要用于高端市场。

据媒体报道,目前台积电CoWoS封装月产8000片,今年底有望提升至11000片,2024年底有望实现14500至16600片左右的月产能,也就是说,想要提升一倍的产量,几乎需要一年半的时间。

摩尔定律见顶 先进封装将成为主流

类似HBM这样以多块芯片堆叠、再通过先进封装粘合起来的解决方案,已成为目前市场上高端芯片的主流设计思路。

背后的原因很简单:先进制程目前已经迭代到7nm、5nm、3nm,技术节点越来越小,生产技术与制造工序越来越复杂,集成电路制造设备的资本投入也就越来越高。

以5nm及更小的制程为例。在这一阶段,受波长限制,普通光刻机的精度已无法满足工艺要求,企业必须转向昂贵的EUV光刻机,一台的售价就高达14亿人民币。

再加上刻蚀和薄膜沉积等设备,5nm制程的设备支出可达31亿美元,是14nm的2倍以上,28nm的4倍左右。

为了成本效益,芯片制造商只能另辟蹊径,从单纯制程工艺的提升,转向通过系统级芯片设计,来提升晶体管密度和性能。

另一方面,过去10年全球数据运算量爆炸式增长,已超越过去40年总和。随着消费电子与车用芯片的需求日益提高,就算芯片制程能达到摩尔定律理论上的物理极限(1nm),仍然无法满足未来产业应用的需求。

而先进封装,因为能同时提高产品性能和降低成本,所以成了后摩尔时代的破局解法。

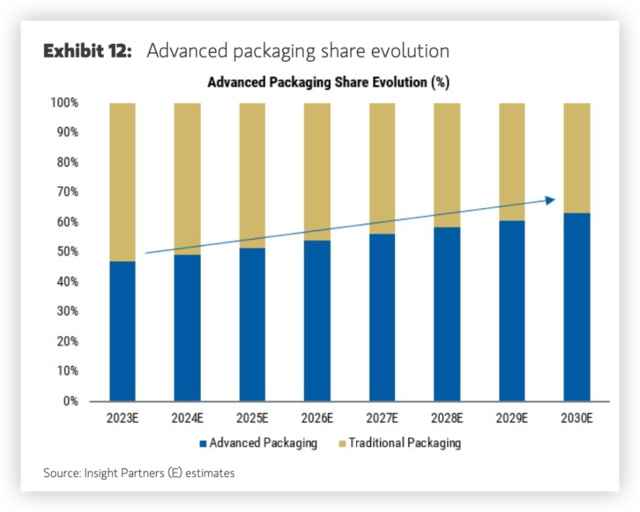

生成式AI催生的庞大需求,已经在加速传统封装向先进封装的迭代。

摩根士丹利指出,AI浪潮正在推动2.5D和3D先进封装技术的大规模应用,到2030年,先进封装将占据整个封装市场60%以上的份额。

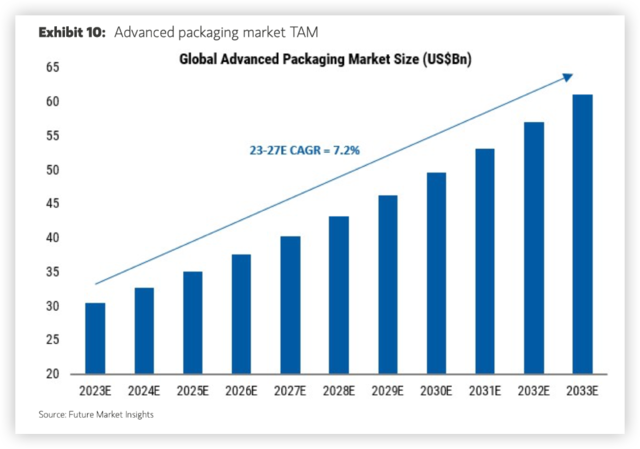

据Future Market Insights测算,当前规模约310亿美元的先进封装市场,将在未来十年内以7.2%的CAGR不断扩张。

摩根士丹利分析师还指出,由于AI芯片增长超显著预期,因此3D/2.5D先进封装预计将以极快的速度增长。2021-2028年的CAGR将达到22%左右。

卡英伟达脖子的厂商已经赚翻了

HBM内存和先进封装领域的两大龙头——SK海力士和台积电,现在已经尝到了甜头。

TrendForce数据显示,尽管在消费电子市场低迷影响下,内存芯片市场出货量和平均销售单价均出现下滑,但HBM产品却在逆势增长,价格一路水涨船高。

有媒体报道称,2023年开年后三星、SK海力士两家存储大厂HBM订单快速增加。SK海力士独家供应的HBM3价格更是上涨5倍。作为原本单位售价就远高于其他规格内存芯片的高毛利产品,HBM3利润之丰厚堪称恐怖。TrendForce预计,AI浪潮带动下,2024年整体HBM营收将达到89亿美元,年增127%。

与此同时,随着英伟达H100、AMD MI300的热销,台积电先进封装同样供不应求。

摩根士丹利分析师表示:

根据我们的代工厂供应链检查,单个CoWoS-S晶圆(及相关工艺)的售价为6,000-12,000美元,具体取决于客户/项目的规模和设计复杂性。根据台积电在Q2财报会议上公开的信息,预计2023年总收入的6-7%将来自先进封装和测试。

我们估计CoWoS今年可能为台积电贡献约10亿美元的收入。由于台积电不断加码CoWoS产能(根据台积电Q2财报电话会上提供的数据,产能将在2024年翻一番),以及当前强劲的AI芯片需求,这一数字可能会进一步增长。因此,我们预计2023-2027年台积电CoWoS收入的CAGR将达到40%。

风险提示及免责条款

市场有风险,投资需谨慎。本文不构成个人投资建议,也未考虑到个别用户特殊的投资目标、财务状况或需要。用户应考虑本文中的任何意见、观点或结论是否符合其特定状况。据此投资,责任自负。

责任编辑:郭明煜

VIP课程推荐

APP专享直播

热门推荐

收起

24小时滚动播报最新的财经资讯和视频,更多粉丝福利扫描二维码关注(sinafinance)