机器之心发布

至强 6 性能核处理器在核数、内存带宽均大幅提升的加持下,推理性能激增,进一步提升了推理的性价比。

至强 6 性能核的核心规模

在之前的文章中,有从业者预测至强 6 性能核处理器每颗计算单元芯片中的内核数量为 43,加上每个计算单元有两组双通道内存控制器各占一个网格,那么总共占用 43+2=45 个网格,可以由 5×9 的布局构成。但这个假设有一个问题,要构成 128 核的 6980P,三颗芯片只屏蔽 1 个内核,这良率要求比较高啊。

至今还未在公开渠道看到至强 6 性能核处理器的 Die shot 或架构图,但英特尔发布了晶圆照片作为宣传素材。虽然晶圆照片并不能提供每颗芯片的清晰信息,但隐约能感觉到,网格构成更像是 5×10,而不是 5×9 或 6×8。另外,左上角和左下角疑似内存控制器的区域面积比预想的要大得多,每一侧占了三个网格。如果接受了两组内存控制器共占用 6 个网格的设定,那么每个芯片中就是 50-6=44 个内核,在构成 6980P 的时候分别屏蔽一到两个核即可,感觉就合理多了。

在获得相对可信的内核数量后,新的疑惑就是:为什么至强 6 性能核的内存控制器这么占地 —— 这个区域有其他未知功能?还是因为增加了 MRDIMM (Multiplexed Rank DIMM) 的支持?毕竟在此之前,英特尔的双通道 DDR5、三通道 DDR4 内存控制器只占一个网格,甚至,连信号规模更大、带宽更高的 HBM 控制器(至强 CPU Max 处理器)也是一个网格。至强 CPU Max 处理器的 HBM2e 是工作在 3,200MT/s,那么每个控制器带宽是 410GB/s,整颗 CPU 有超过 2TB/s 的 HBM 带宽。

虽然对疑似内存控制器区域所占芯片面积的疑惑未解,还需要进一步解惑,但至少可以确定,英特尔在这一代至强的内存控制器上是下了大本钱的。至少在相当一段时间内,它是可以 “独占” MRDIMM 的优势了。

至强 6 性能核的 NUMA 与集群模式

谈服务器的内存就绕不过 NUMA(Non-Uniform Memory Access,非统一内存访问)。因为随着 CPU 内核数量的增加,各内核的内存访问请求冲突会迅速增加。NUMA 是一个有效的解决方案,将内核分为若干组,分别拥有相对独立的缓存、内存空间。规模缩小后,冲突就会减少。一般来说,NUMA 划分的原则是让物理上临近某内存控制器的内核为一个子集。这个子集被英特尔称为 SUB-NUMA Clustering,简称 SNC。同一 SNC 的内核绑定了末级缓存(LLC)和本地内存,访问时的时延最小。

譬如,在第三代至强可扩展处理器中,一个 CPU 内可划分两个 SNC 域,每个 SNC 对应一组三通道 DDR4 内存控制器。如果关闭 NUMA,那么整个 CPU 的内存将对称访问。

而第四代至强可扩展处理器使用了 4 颗芯粒的封装,可以被划分为 2 个或 4 个 SNC 域。如果希望每个内核可以访问所有的缓存代理和内存,可以将第四代至强可扩展处理器设置为 Hemisphere Mode 或者 Quadrant Mode,默认是后者。第五代至强可扩展处理器是 2 颗芯粒,可以划分为两个 SNC 域。

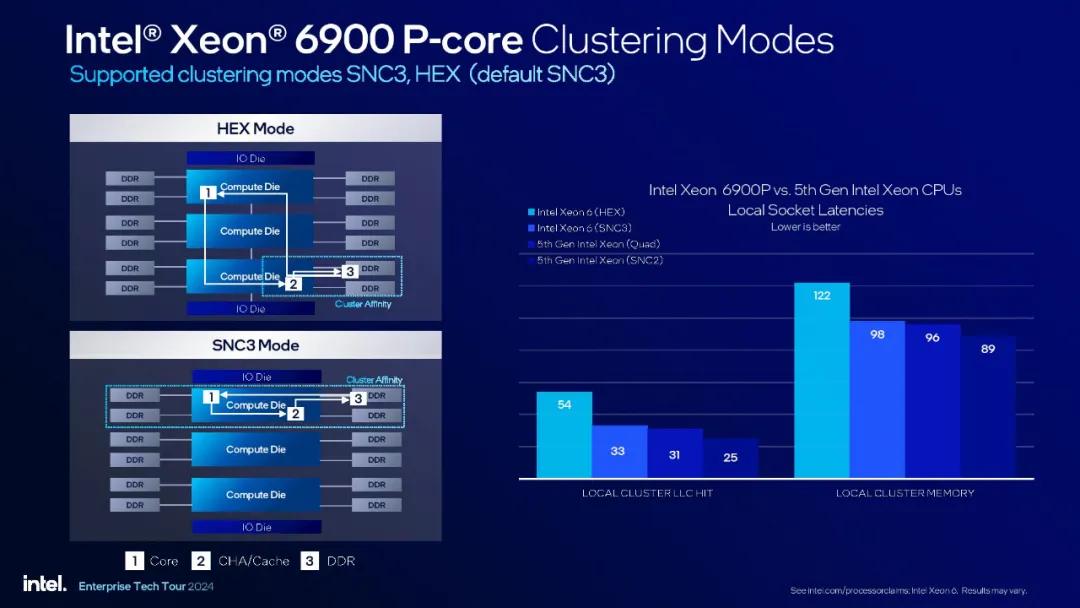

在至强 6 性能核中,可以将每个计算单元芯片作为一个 SNC,每个域拥有 4 个内存通道,这被称为 SNC3 Mode。如果要通过其他芯粒的缓存代理访问所有内存,那就是 HEX Mode。

根据英特尔提供的数据,几种不同模式的内存访问时延差异较大,与内核、内存控制器之间的 “距离” 直接相关。至强 6 性能核的内核规模、内存控制器数量增加之后,相应的访问时延也会上升。例如,根据前面的观察,至强 6 性能核内每个计算单元芯片中,内核与内存控制器的最远距离为 10 列,而第四代 / 第五代至强可扩展处理器无 NUMA 的为 8 列。这反映在英特尔的数据上,就是至强 6900P 在 SNC3 Mode 的时延略高于上一代至强处理器的 Quad Mode。如果至强 6900P 设为 HEX Mode,那么内核与内存控制器的最远距离将达到 13 甚至 15 列,时延增加会比较明显。

整体而言,由于 SNC3 Mode 时延低,其将成为至强 6 服务器的默认模式。这种模式主要是适合虚拟化 / 容器化这类常见云应用,以及并行化程度高的计算(如编解码)等。当然,HEX Mode 可以直接访问更大规模的内存,这对于大型数据库,尤其是以 OLTP 为代表的应用来说更为有利。Oracle 和 SQL 通常建议关闭 NUMA 以获得更佳的性能。Apache Cassandra 5.0 这类引入向量搜索的数据库也能从 HEX Mode 显著获益。部分科学计算也更适合 HEX Mode,譬如通过偏微分方程建模的 PETSs、分子动力学软件 NAMD 等。

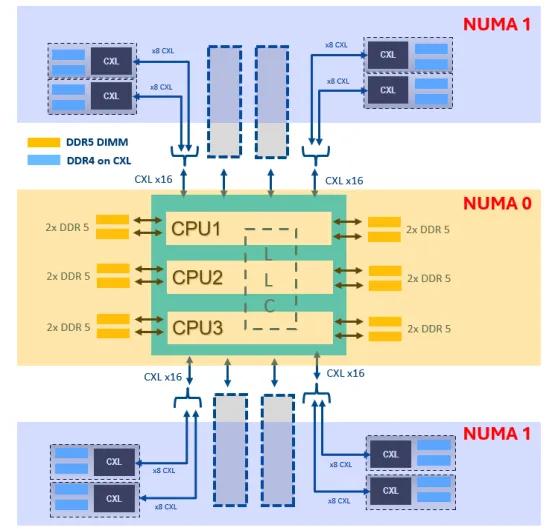

HEX Mode 的另一个典型场景是配合 CXL 内存使用。譬如英特尔在今年 12 月 11 日发布的一篇利用 CXL 内存优化系统内存带宽的论文中,使用了至强 6900P 搭配 12 条 64GB DDR5 6400 以及 8 个 128GB CXL 内存模块,其中至强 6900P 本地的 768GB DDR5 内存在 HEX Mode 下配置为 NUMA0,所有的 1TB CXL 内存配置为 NUMA1,采用优化交错配置(Interleaving Strategy)。测试表明,在内存带宽敏感的应用中,使用 CXL 内存扩展可以提升 20%~30% 的性能。

MRDIMM 领跑者

对于至强 6 性能核处理器而言,提升内存带宽最直接的方法莫过于 MRDIMM。这也是这款处理器相比其他同类产品比较独占的一项能力,近期看不到任何其他 CPU 厂商有明确支持 MRDIMM 的时间表,更不要说推出实际产品了。相对而言,内存厂商对 MRDIMM 的支持比较积极,美光、SK 海力士、威刚都推出了相应的产品,包括高尺寸(Tall formfactor,TFF)。第一代 DDR5 MRDIMM 的目标速率为 8,800 MT/s,未来会逐步提升至 12,800 MT/s、17,600 MT/s。

MRDIMM 增加了多路复用数据缓冲器(MDB),改进了寄存时钟驱动器(MRCD)。MDB 布置在内存金手指附近,与主机侧的 CPU 内存控制器通讯。MDB 主机侧的运行速度是 DRAM 侧的双倍,DRAM 侧的数据接口是主机侧的双倍。MRCD 可以生成 4 个独立的芯片选择信号(标准的 RCD 是两个,对应两个 Rank)。MDB 可通过两个数据接口将两个 Rank 分别读入缓冲区,再从缓冲区一次性传输到 CPU 的内存控制器,由此实现了带宽翻倍。

由于 MRCD 可以支持 4 个 Rank,也意味着可以支持双倍的内存颗粒。已经展示的 MRDIMM 普遍引入更高的板型(TFF),单条容量也由此倍增。由于至强 6900P 插座尺寸大增,导致双路机型的内存槽数量从上一代的 32 条减少到 24 条。要能够继续扩展内存容量,增加内存条的面积(增加高度)确实是最简单直接的手段。通过使用 256GB 的 MRDIMM,双路至强 6900P 机型可以获得 6TB 内存容量。除了更大的内存带宽,更高的内存容量也非常有利于 AI 训练、大型数据库等应用的需求,进一步强化至强 6900P 在 AI 机头领域的优势。

与 DDR5 6,400MT/s 相比,MRDIMM 8,800MT/s 的实际运行频率略低(4,400MT/s),导致轻量级的应用不能从内存带宽的增加当中明显获益。其实类似的问题在内存代际转换之初均会存在,能够充分利用更大内存带宽的主要还是计算密集的应用,譬如加密、科学计算、信号处理、AI 训练和推理等。从目前的测试看,对 MRDIMM 受益最大的应用主要包括 HPCG(High Performance Conjugate Gradient)、AMG(Algebraic Multi-Grid)、Xcompact3d 这些科学计算类的应用,以及大语言模型推理。

内存带宽与大模型推理

上一节有提到,并非所有应用都能充分利用 MRDIMM 的内存带宽收益。就本节重点要谈的推理应用而言,根据目前所见的测试数据,卷积神经网络为代表的传统推理任务在 MRDIMM 中获得的收益就比较小,不到 10% 的水平。而在大语言模型推理当中,MRDIMM 的带宽优势将得到充分的发挥,性能提升在 30% 以上,因为大模型是确定性的渴求显存 / 内存容量和带宽的应用场景。

在这里就得提一下英特尔至强 6 性能核处理器发布会资料中的另一个细节:在多种工作负载的性能对比中,AI 部分的提升幅度最为明显,而且仅用了 96 核的型号(至强 6972P)。

也就是说,至强 6972P 使用了至强 8592 + 的 1.5 倍内核,获得了至少 2.4 倍的大语言模型推理性能。其中,右侧的是 Llama3 8B,int8 精度,那么模型将占用约 8GB 的内存空间。以目前双路 24 通道 MRDIMM 8,800MT/s 约 1,690GB/s 的总内存带宽而言,可以算出来每秒 token 数理论上限是 211。而双路 8592 + 是 16 通道 DDR5 5,600MT/s,内存总带宽为 717GB/s,token 理论上限是接近 90。二者的理论上限正好相差大约 2.4 倍。在这个例子当中,内存带宽的增长幅度明显大于 CPU 内核数量的增长。也就是说,在假设算力不是瓶颈的情况下,内存或显存容量决定了模型的规模上限,而带宽决定了 token 输出的上限。

一般来说,在控制模型参数量并进行低精度量化(int8 甚至 int5、int4)之后,大语言模型推理时的算力瓶颈已经不太突出,决定并发数量和 token 响应速度的,主要还是内存的容量和带宽。通过 MRDIMM,以及 CXL 内存扩展带宽将是提升推理性能最有效的方式。这也是目前 CPU 推理依旧受到重视的原因,除了可获得性、资源弹性外,在内存容量及带宽的扩展上要比 VRAM 便宜的多。

结语

随着掌握更多的信息,至强 6 性能核处理器在内存带宽上的优势和潜力显得愈发清晰了。MDRIMM 不但能够大幅提升内存带宽,还能使可部署的内存容量翻倍,显著利好传统的重负荷领域,如科学计算、大型数据库、商业分析等,对于新兴的向量数据库也大有裨益。CXL 还能够进一步起到锦上添花的作用。

过去几年,增长迅猛的大模型推理需求,让至强可扩展处理器(从第四代开始)利用 GPU 缺货的契机证明了在 AMX 的加持下,纯 CPU 推理也有不错的性能,而且易于采购和部署。随着应用深入,部分互联网企业还挖掘了 CPU 推理的资源弹性,与传统业务同构的硬件更易于进行峰谷调度。至强 6 性能核处理器在核数、内存带宽均大幅提升的加持下,推理性能激增,进一步提升了推理的性价比。在解决了 “能或不能” 的问题之后,推理成本是大语言模型落地后最关键的挑战。或许在这方面,至强 6 性能核处理器配 MRDIMM 的组合,将会带来一些新的解题思路。

“掌”握科技鲜闻 (微信搜索techsina或扫描左侧二维码关注)