台积电OIP(开放创新平台)于美西当地时间25日展开,除表扬包括力旺、M31在内之业者外,更计划推出3Dblox新标准,进一步加速3D IC生态系统创新,并提高EDA工具的通用性。 台积电设计构建管理处负责人Dan Kochpatcharin表示,将与OIP合作伙伴一同突破3D IC架构中的物理挑战,帮助共同客户利用最新的TSMC 3DFabric技术实现优化的设计。

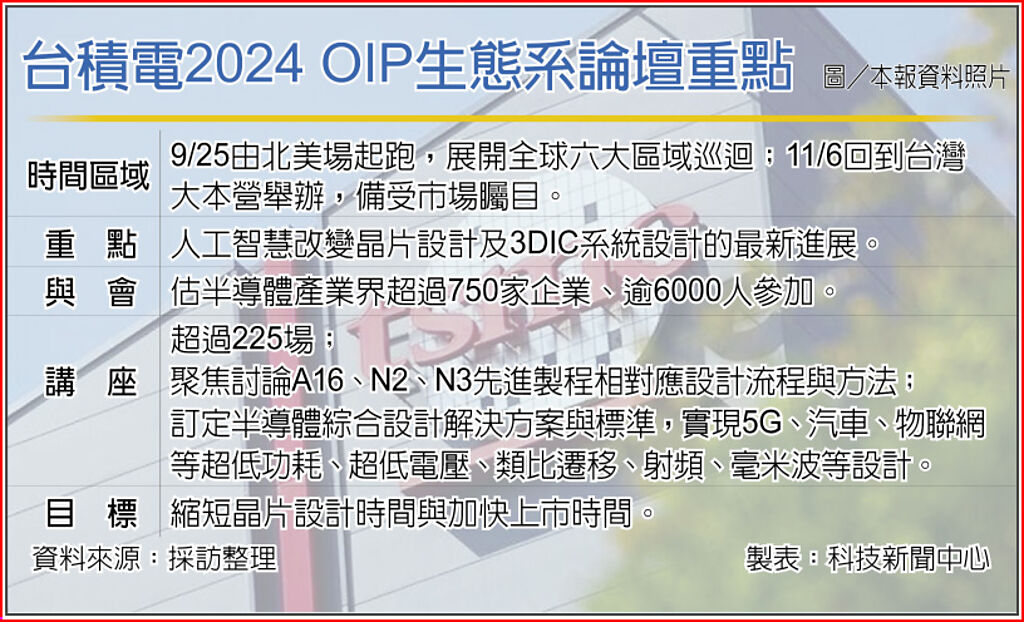

台积电OIP生态系统论坛今年由北美站起跑,与设计合作伙伴及客户共同探讨如何通过更深层次的合作,推动AI芯片设计的创新。 Dan Kochpatcharin强调,「我们正在迎来一个AI驱动的时代,对高效能AI芯片的需求在数据中心等领域不断攀升。 台积的技术创新正在为人工智能解锁巨大潜力。」

利用AI和机器学习技术,显著提高3D IC设计的生产力,并优化设计的功耗、性能和面积(PPA),以及设计结果的质量(QoR)。 透过与OIP伙伴的紧密合作,台积电正在解决3D IC架构物理现象的挑战,并利用最新的台积电3DFabric技术推动创新。

台积电作为3Dblox委员会核心成员,积极推动3Dblox标准的发展。 台积电透露,计划将该标准通过IEEE公开发布,使更多的合作伙伴、客户和晶圆厂更容易使用3Dblox,推动AI技术的发展。

AWS、博通(Broadcom)及Socionext等公司均对台积电的技术创新表示赞赏。 其中,博通更于本月推出业界首款基于台积电5纳米制程的Face-to-Face 3D SoIC装置,采用3D堆叠和CoWoS-R封装技术,整合9个芯片和六个HBM堆叠,为2025年即将进行的3D SoIC量产奠定基础。

台积电硅智财合作伙伴力旺之NeoFuse OTP在台积电N7与N6成功量产、并赢得N5、N5A、N4P节点的设计案; M31更宣布ONFi5.1 I/O IP在台积电5纳米制程平台上成功完成硅验证,并向3纳米持续发展。

透过与OIP伙伴紧密合作,台积电积极推动3D IC设计的创新,致力于为全球市场提供最先进的AI芯片解决方案; 随着技术的不断演进,台积电继续引领半导体产业的发展,为未来AI应用提供无限可能。

本文引用地址:

“掌”握科技鲜闻 (微信搜索techsina或扫描左侧二维码关注)