在高压开关电源应用中,相较传统的硅MOSFET和IGBT,碳化硅(以下简称“SiC”)MOSFET 有明显的优势。使用硅MOSFET可以实现高频(数百千赫兹)开关,但它们不能用于非常高的电压(>1 000 V)。而IGBT 虽然可以在高压下使用,但其 “拖尾电流 “和缓慢的关断使其仅限于低频开关应用。SiC MOSFET则两全其美,可实现在高压下的高频开关。然而,SiC MOSFET 的独特器件特性意味着它们对栅极驱动电路有特殊的要求。了解这些特性后,设计人员就可以选择能够提高器件可靠性和整体开关性能的栅极驱动器。在这篇文章中,我们讨论了SiC MOSFET 器件的特点以及它们对栅极驱动电路的要求,然后介绍了一种能够解决这些问题和其他系统级考虑因素的IC 方案。

本文引用地址:

SiC MOSFET特性

与硅器件相比,SiC MOSFET 的跨导(增益)更低,内部栅极电阻更高,其栅极导通阈值可能低于2 V。因此,在关断状态下,必须向SiC MOSFET 施加负栅源电压(通常为-5 V)。SiC 器件的栅源电压通常要求在18 V ~ 20 V,以降低导通状态下的导通电阻(RDS)。SiC MOSFET 工作在低VGS 下可能会导致热应力或由于高RDS 而可能导致故障。与低增益相关的其他影响会直接影响几个重要的动态开关特性,在设计适当的栅极驱动电路时必须考虑这些影响,包括导通电阻、栅极电荷(米勒平台)和过电流(DESAT)保护。

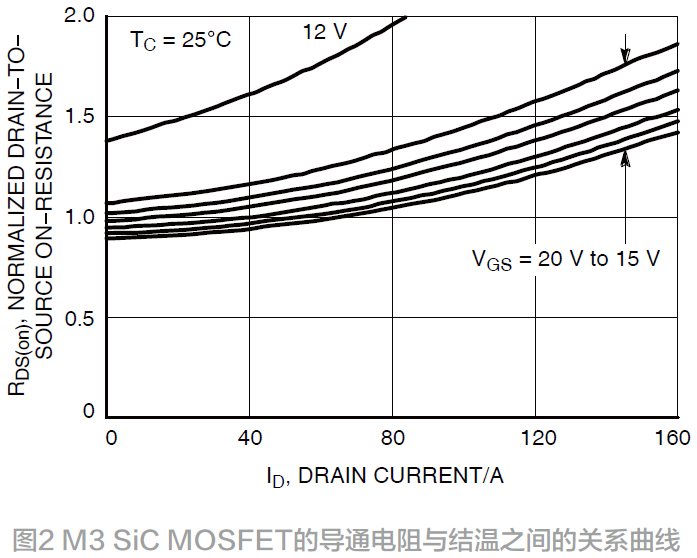

导通电阻

在低VGS 时,一些SiC 器件的导通电阻与结温特性之间的关系曲线看起来是抛物线*(由于内部器件特性的组合)。(* 这适用于安森美M1 和M2 SiC MOSFET。)当VGS = 14 V 时,RDS 似乎具有负温度系数(NTC) 特性,即电阻随温度升高而降低。SiC MOSFET 的这一独特特征直接归因于其低增益,这意味着如果两个或更多的SiC MOSFET 并联工作在低VGS( 负温度系数) 下,可能会导致灾难性损坏。因此,只有当VGS 足以确保可靠的正温度系数工作时(即VGS > 18 V),才建议将SiC MOSFET 并联工作。

图1 M1或M2 SiC MOSFET的导通电阻与结温之间的关系曲线

图1 M1或M2 SiC MOSFET的导通电阻与结温之间的关系曲线新一代M3 SiC 在所有VGS 和所有温度范围都显示正温度系数

栅极电荷

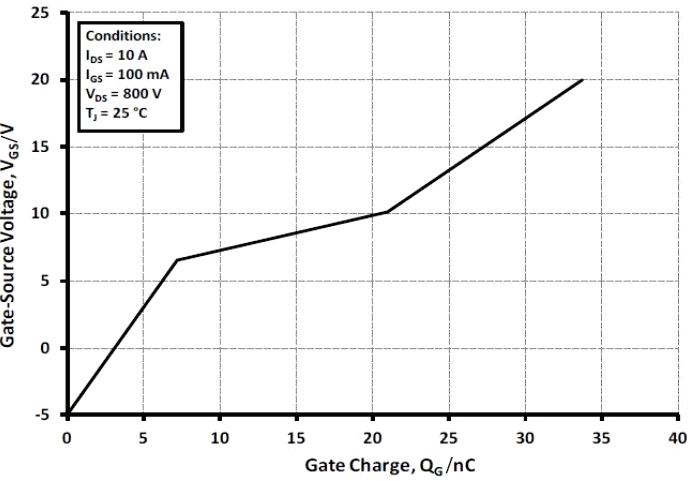

向SiC MOSFET 施加栅源电压 (VGS) 时,电荷被传输以尽快使VGS 从VGS (MIN) (VEE) 和VGS (MAX)(VDD) 升高。由于器件的内部电容是非线性的,因此可以使用VGS 与栅极电荷(QG)的关系曲线来确定在给定的VGS 下必须传输多少电荷。SiC MOSFET 的这种 “米勒平台“发生在较高的VGS 上,而且不像硅MOSFET 那样平坦。不平坦的米勒平台意味着在相应的电荷范围内,VGS 不是不变的,这也是由于器件低增益导致的。同样值得注意的是,QG = 0 nC(关断SiCMOSFET 所需的电荷量)不会发生在VGS = 0 V 时,因此VGS 必须为负(本例中为-5 V),以使栅极完全放电。

由于我们想测量导通或关断SiC MOSFET 所需的电荷量,我们的曲线只绘制了Qg 的增量(或Qg 的累积或Qg 的变化)。这个数值也叫Qg。这可能会引起混淆。我们需要将这张图解读为需要的能量,而不纯粹是存储在栅源电容器中的能量。

图3 SiC MOSFET栅源电压与栅极电荷的关系

图3 SiC MOSFET栅源电压与栅极电荷的关系使用负栅极驱动阻断电压主要是为了减少关断状态下的漏电流。这也是由于跨导增益低造成的。使用负的阻断电压还可以减少开关损耗,主要是在关断期间的开关损耗。

因此,几乎对于所有的SiC MOSFET,都建议在关断状态下使用的最小VGS 为-5 V < VGS (MIN) < -2 V,有些制造商规定电压低至-10 V。

欠压保护(DESAT)

DESAT 保护是一种过电流检测,起源于IGBT 的驱动电路。在导通时,如果IGBT 不能再保持饱和状态(“去饱和”),集电极- 发射极电压就会上升,同时全集电极电流流过。显然,这对效率有不利影响,在最坏的情况下,可能导致IGBT 的灾难性故障。所谓的“DESAT“功能监测IGBT 的集电极- 发射极电压,并检测何时出现潜在的破坏性条件。虽然SiC MOSFET 中的故障机制有些不同,但会有类似的情况,在最大ID 流过时VDS 可能上升。如果导通期间的最大VGS 太低,栅极驱动导通沿太慢,或者存在短路或过载情况,就会出现这种不理想的条件。在满载ID 的情况下,RDS 会增加,导致VDS意外上升。当SiC MOSFET发生欠饱和事件时,VDS 的反应非常迅速,而最大漏极电流继续流过不断增加的导通电阻。当VDS 达到预定的阈值时,就可以激活保护。应特别注意避免感测VDS 的延迟,因为延迟会掩盖这种现象。因此,DESAT 是栅极驱动电路的一个重要的辅助性保护。

动态开关

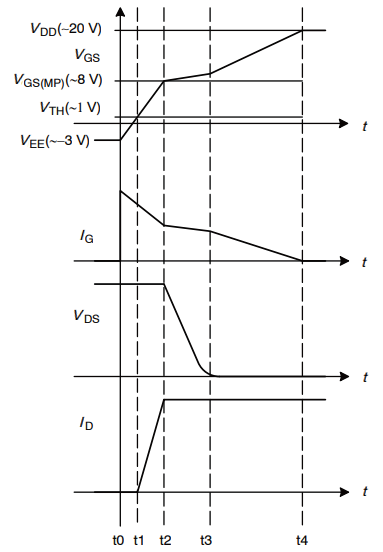

SiC MOSFET 的导通和关断状态有4 个不同的阶段。所示的动态开关波形呈现的是理想工作条件的情况。然而,在实践中,封装寄生物,如引线和邦定线电感、寄生电容和PCB 布局会极大地影响实际波形。合适的器件选择、最佳的PCB 布局,以及对设计好的栅极驱动电路的重视,对于优化开关电源应用中使用的SiCMOSFET 的性能都是至关重要的。

栅极驱动电路的设计要求

为了补偿器件低增益,同时实现高效、高速的开关,对SiC 栅极驱动电路有以下关键要求。

● 对于大多数SiC MOSFET,驱动电压在-5 V >VGS > 20 V 之间时性能最佳。栅极驱动电路应能承受VDD = 25 V 和VEE = -10 V,以适用于最广泛的可用器件。

● VGS 必须有快速的上升沿和下降沿( 在几ns 范围内)。

● 在整个米勒平台区域内,有能力提供高的峰值栅极灌电流和拉电流(数A)。

● 当VGS 下降到米勒平台以下时,需要提供一个非常低的阻抗保持或 “钳位”,以实现高的灌电流能力。

灌电流的额定值应超过仅对SiC MOSFET 的输入电容放电所需的电流。10 A 左右的峰值灌电流最小额定值应适用于高性能、半桥电源拓扑结构。

● VDD 欠压锁定(UVLO)水平,与开关开始前VGS > ~16 V 的要求相匹配。

● VEE UVLO 监测能力确保负电压轨在可接受的范围内。

● 能够检测、报告故障和提供保护的去饱和功能,使SiC MOSFET 长期可靠运行。

● 支持高速开关的低寄生电感。

● 小尺寸驱动器封装,布局尽可能靠近SiC MOSFET。

图4 SiC MOSFET导通序列的4个阶段

图4 SiC MOSFET导通序列的4个阶段栅极驱动器方案

安森美的NCP51705 是一款SiC 栅极驱动器IC,提供高的设计灵活度和集成度,几乎与任何SiC MOSFET兼容。NCP51705 集成许多通用栅极驱动器IC 所共有的功能,包括:

● VDD 正电源电压最高28 V;

● 高峰值输出电流——6 A 拉电流和10 A 灌电流;

● 内置5 V 基准可用于偏置5 V、20 mA 以下的低功耗负载(数字隔离器、光耦合器、微控制器等);

● 单独的信号和电源接地连接;

● 单独的源和灌输出引脚;

● 内置热关断保护;

● 单独的非反相和反相TTL、PWM 输入。

图5 NCP51705 SiC栅极驱动器框图

图5 NCP51705 SiC栅极驱动器框图然而,该IC 集成几个独特的功能,能够以最少的外部元器件设计出可靠的SiC MOSFET 栅极驱动电路。这些功能包括:

● 欠压保护(DESAT);

● 电荷泵(用于设置负电压轨);

● 可编程的欠压锁定(UVLO);

● 数字同步和故障报告;

● 24 引脚,4 mm×4 mm,热增强型MLP 封装,便于板级集成。

总结

在选择合适的栅极驱动器IC 时,SiC MOSFET 的低增益给设计人员带来了难题。通用的低边栅极驱动器不能高效和可靠地驱动SiC MOSFET。NCP51705 集成一系列功能,为设计人员提供了一个简单、高性能、高速的解决方案,高效、可靠地驱动SiC MOSFET。

(本文来源于《电子产品世界》杂志2023年4月期)

“掌”握科技鲜闻 (微信搜索techsina或扫描左侧二维码关注)